| 崁丂丂丂丂栚 |

婰丂丂丂丂丂丂丂帠 |

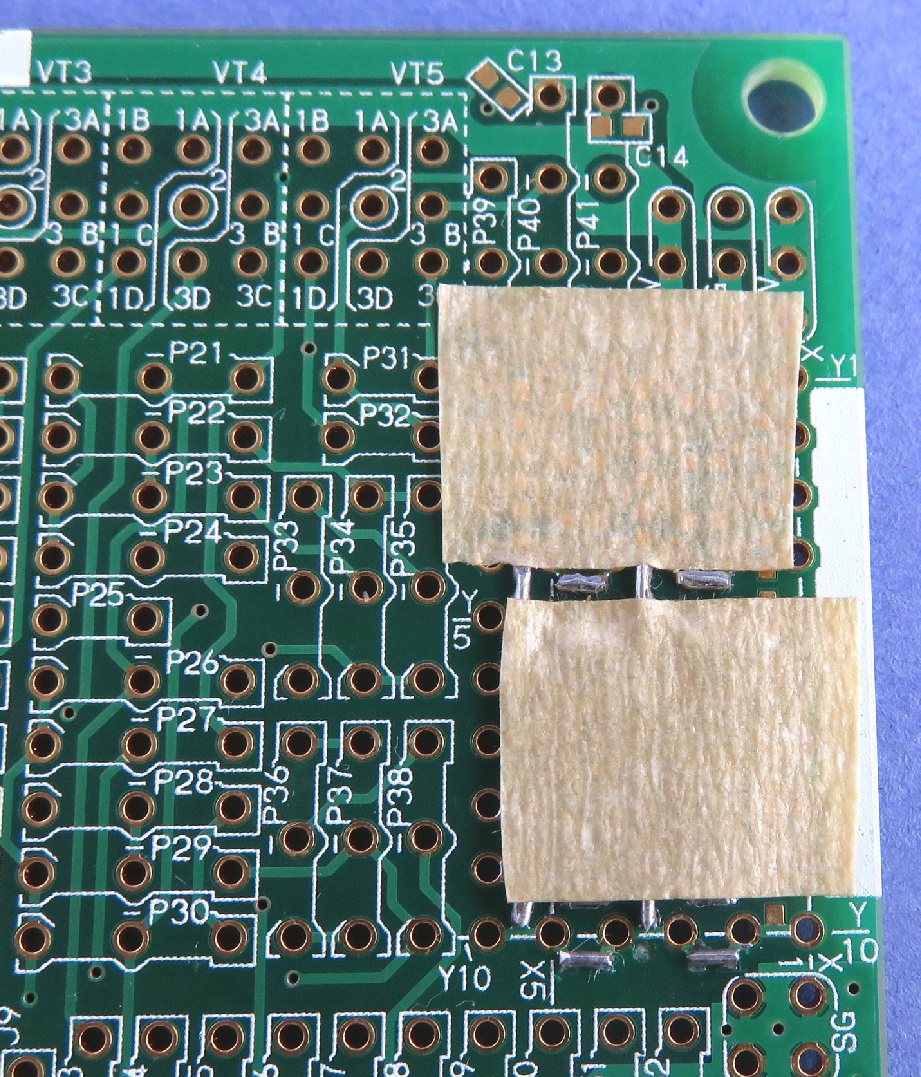

幚梡乮幚愴乯岦偗僠僢僾晹昳偺偼傫偩晅偗曽朄

|

昞柺幚憰偼傫偩晅偗偑丄弶怱幰偱傕梕堈偵偱偒傞曽朄傪彂偄偨傕偺偱偡丅

媄弍帒椏 彫宍僠僢僾晹昳偺偼傫偩晅偗偑梕堈丂L宆偙偰愭偵傛傞揰娽偼傫偩朄乿

|

SMD僋儔儞僾偺棙梡

|

昞柺幚憰偼傫偩晅偗梡僣乕儖乽SMD僋儔儞僾乿乿偼昞柺幚憰晹昳偺偼傫偩晅偗偵戝曄曋棙偱偡丅

昞柺幚憰偼傫偩晅偗梡僣乕儖乽SMD僋儔儞僾乿乿偼昞柺幚憰晹昳偺偼傫偩晅偗偵戝曄曋棙偱偡丅

昞柺幚憰晹昳傪偼傫偩晅偗梡僷僢僪偵埵抲寛傔偟屌掕乮僋儔儞僾乯偡傞偺偱丄屻偼備偭偔傝偼傫偩晅偗偡傞偩偗偱偡丅

摿偵弶怱幰偵偼偍慐傔偱丄堦搙巊偭偨傜庤曻偣側偔側傝傑偡丅

|

|

僠僃僢僋抂巕庢傝晅偗

|

帋嶌夞楬偱偼僠僃僢僋抂巕偼岠棪傪忋偘傞堊偵廳梫偱偡丅

尋媶奐敪梡婎斅偱偼夞楬僷僞乕儞偼愙懕偝傟偰偄偰傕幚憰偟側偄晹昳偺僗儖乕儂乕儖傪梡偄偰娙扨偵僠僃僢僋抂巕傪庢傝晅偗傜傟傑偡丅

傑偨丄夞楬峔惉梡偺僕儍儞僷慄傪倀帤宆偵偡傟偽僠僃僢僋抂巕偲偟偰傕巊梡偱偒丄僐僗僩僛儘偱偡丅

|

|

奐敪婡婍乮應掕婍乯梡僌儔儞僪僶乕

|

僼傽儞僋僔儑儞僕僃僱儗乕僞丄僆僔儘僗僐乕僾丄僨傿僕僞儖儅儖僠儊乕僞摍暋悢偺奐敪婡婍傗應掕婍傪愙懕偡傞応崌偼懡偔偺僌儔儞僪抂巕偑昁梫偵側傝傑偡丅

尋媶奐敪梡婎斅偵偼懡偔偺僌儔儞僪僗儖乕儂乕儖偑桳傞偺偱丄冇侽丏俇倣倣掱搙偺扨慄傪儐僯僶乕僒儖僄儕傾偵愝偗丄僌儔儞僪僗儖乕儂乕儖偵愙懕偡傟偽梕堈偵婡婍梡僌儔儞僪僶乕乮僶僗乯傪摼傜傟傑偡丅

俠俫俬俹乛俢俬俹寭梡儀乕僗儐僯僶乕僒儖婎斅 俹倃侾俁侾侽偺婎斅抂傗丄戝宎儕乕僪梡儐僯僶乕僒儖婎斅俹倃侾俀俀侽偱偼冇侾丏侽倣倣偺扨慄偑巊梡偱偒傞偺偱婃忎偱戝偒傔偺僌儔儞僪僶乕偑愝偗傜傟傑偡丅

丂 丂

丂 丂

|

|

揹尮僀儞僕働乕僞

|

揹尮僆儞乛僆僼忬懺偑堦栚偱敾傞揹尮僀儞僕働乕僞偼桳傟偽曋棙偱偡丅

尋媶奐敪梡婎斅偺揹尮僗儖乕儂乕儖丄僌儔儞僪僗儖乕儂乕儖偲儐僯僶乕僒儖僄儕傾傪棙梡偡傞偲娙扨偵俴俤俢偑幚憰偱偒傑偡丅

婎斅偵傛偭偰偼偦傟傜偑嬤愙偟偰偄傞偺偱丄攝慄柍偟偱俴俤俢偲掞峈傪幚憰偡傞偩偗偱揹尮僀儞僕働乕僞偑慻傔傑偡丅

丂 丂

|

|

儕乕僪慄偺嵞棙梡

|

儕乕僪僞僀僾偺晹昳幚憰屻偵僇僢僩偟偨儕乕僪傪曐娗偟偰偍偄偰夞楬峔惉梡偺僕儍儞僷慄偵梡偄傞偲曋棙偱偡丅

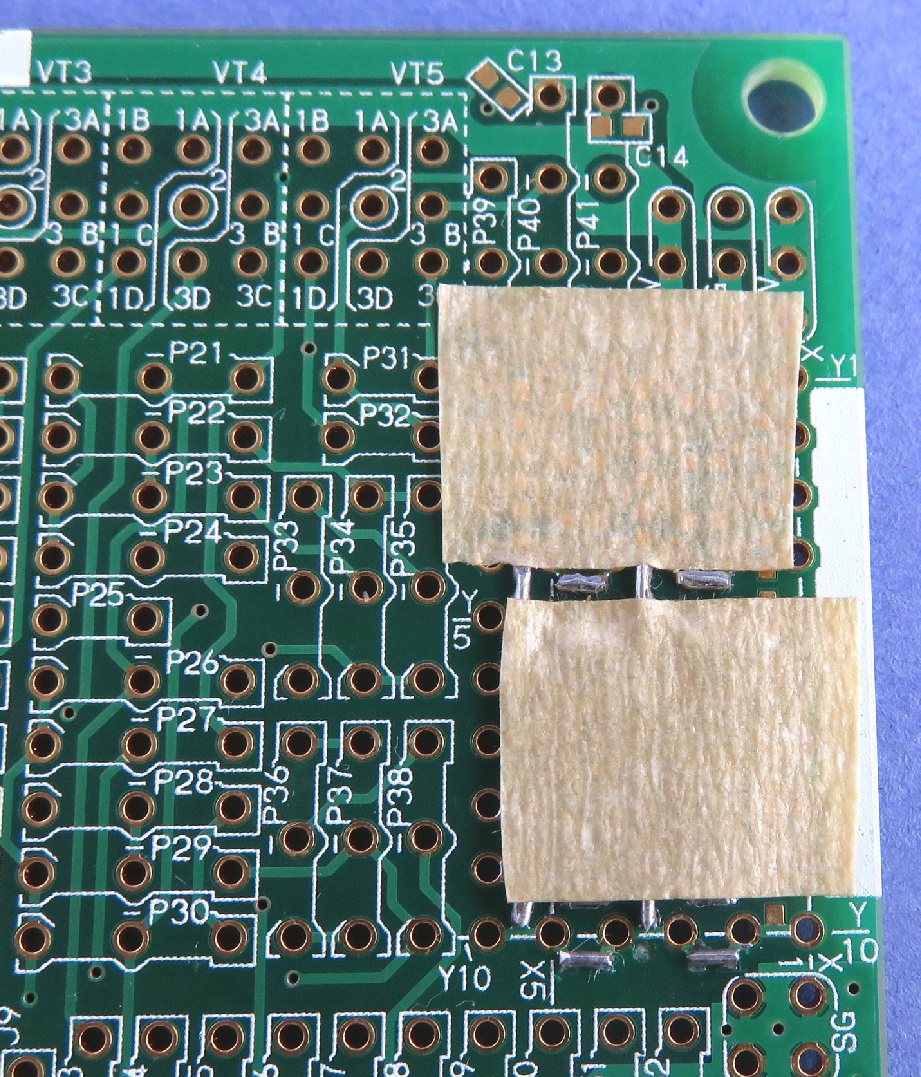

幨恀偼儕乕僪慄傪僇僢僩偡傞嵺偵丄柤巋偺嬻偒敔偵挋傔崬傫偩傕偺偱偡丅

|

|

愨墢梡掙斅偺嶌惉

|

婎斅偱帋尡帯嬶傪惢嶌偡傞嵺偵丄廃埻偲揹婥揑偵愨墢偡傞堊偵丄愨墢梡偺掙斅傪愝偗傞応崌偑彮側偐傜偢桳傝傑偡丅

丂婎斅偵崌傢偣偨愨墢梡掙斅傪丄梊傔傑偲傔偰惢嶌偟偰偍偔偲曋棙偱偡丅

丂婎斅偵崌傢偣偨愨墢梡掙斅傪丄梊傔傑偲傔偰惢嶌偟偰偍偔偲曋棙偱偡丅

丂岤偝1mm埲壓偺傾僋儕儖斅偱偁傟偽丄僴儞僪僇僢僞偱娙扨偵僇僢僩偱偒傑偡丅

丂栜榑庢傝晅偗傞堊偺巟拰傗價僗傕僾儔僗僠僢僋惢偵偟傑偡丅

|

儕乕僪儀儞僟

|

僕儍儞僷慄丄儕乕僪晹昳偺儕乕僪嬋偘壛岺偵偼儕乕僪儀儞僟俼俛亅俀丄俼俛亅俆乮僒儞僴儎僩乯偑曋棙乮偲偄偆傛傝傓偟傠昁恵乯偱偡丅

|

|

僠僢僾晹昳梡僺儞僙僢僩丂

|

埲慜壓婰偺SMD僺儞僙僢僩傪偛徯夘偟傑偟偨丅

偟偐偟丄尰嵼儊乕僇偝傫偺儂乕儉儁乕僕偐傜偼嶍彍偝傟偰偄傞條偱丄梋傝巟帩偝傟側偐偭偨偺偐傕偟傟傑偣傫丅

偦偺屻丄僠僢僾晹昳暣幐懳嶔偵偼僺儞僙僢僩偵僼儔僢僋僗傪揾晍偡傞曽朄偑桳岠側帠偑敾傝傑偟偨偺偱丄尰嵼偼

僺儞僙僢僩偵僼儔僢僋僗傪揾晍偟偰抲偔曽朄傪偍慐傔偟偰偍傝傑偡丅

*****乮埲慜偛徯夘乯*************

堦斒揑側僺儞僙僢僩偱偼愲偭偨愭抂偑彮偟擯傟偨偩偗偱僠僢僾晹昳偼壗張偐偵旘傫偱峴偒丄扵偡帪娫僐僗僩偐傜戝掞偺応崌偼峴曽抦傟偢偵側傝傑偡丅

SMD僺儞僙僢僩 PT-20乮姅幃夛幮丂僄儞僕僯傾乯偼僠僢僾晹昳傪妋幚偵儂乕儖僪偱偒丄峴曽晄柧偑戝暆偵尭傞偺偱偍彠傔昳偱偡丅

僠僢僾晹昳偺儂乕儖僪傪慜幰偑俀揰偱峴側偆偺偵懳偟偰丄屻幰偼係揰偱峴側偆帠偵場傞傕偺偲峫偊傟偽擺摼偱偒傑偡丅

|

|

敿揷晅偗偵娭偡傞忣曬

|

敿揷晅偗傪楙廗偡傞偵偟偰傕岆偭偨帺屓棳偵娮傝堈偄偺偱梫拲堄偱偡丅

僀儞僞乕僱僢僩偱扵偡偲敿揷晅偗怑恖偺敿揷晅偗島嵗乮僲僙惛婡乯丄

俠俻弌斉幮丄奺敿揷僐僥儊乕僇摍偺僒僀僩偵敿揷晅偗偺摦夋偑懡悢桳傝丄戝曄嶲峫偵側傝傑偡丅

偦偺拞偱傕摿偵敿揷晅偗怑恖偺敿揷晅偗blog傗儊乕儖儅僈僕儞偼棟榑揑偵傕幚慔揑偵傕

敿揷晅偗娭楢偺忣曬偑枮嵹偱弶怱幰偵偼戝曄堊偵側傝傑偡丅

偍栚偵妡偐偭偨帠偼偁傝傑偣傫偑僒僀僩傪塣塩偡傞栰悾巵偼昅偑棫偪丄懡寍懡嵥偺曽偺條偱丄偦偺庤偼偝偟偢傔乭僑僢僪僴儞僟乭丠丏丏丏

|

|

僼儔僢僋僗偼昁恵

|

昞柺幚憰晹昳偺敿揷晅偗偵偼僼儔僢僋僗偑昁梫偲尵傢傟傑偡偑丄僼儔僢僋僗擖傝偺巺敿揷偱廩暘側儕乕僪晹昳偺敿揷晅偗偺宱尡偐傜丄曇幰傕娷傔敿怣敿媈偺恖偑懡偄偲巚傢傟傑偡丅

偟偐偟丄昞柺幚憰晹昳偺敿揷晅偗偺巇忋偑傝偑崱堦偮側偺偱丄帋偟偵僼儔僢僋僗傪巊梡偟偨張丄栚偐傜僂儘僐揑偵巇忋偑傝偑椙偔側傝傑偟偨丅

傗偼傝僼儔僢僋僗偼昞柺幚憰晹昳偺敿揷晅偗偵偼昁恵偺條偱偡丅

偙偺帠偼敿揷晅偗怑恖偺敿揷晅偗島嵗乮僲僙惛婡乯偱傕岥傪巁偭傁偔偡傞條偵偟偰愢偐傟偰偄傑偡丅

夰媈攈偺曽偵偼丄閤偝傟偨偲巚偭偰堦搙帋偝傟傞帠傪偍彠傔偟傑偡丅

|

|

僼儔僢僋僗愻忩嵻傕

|

僼儔僢僋僗傪巊梡偟偨傜屻偺僩儔僽儖杊巭偺堊偵愻忩嵻偱棊偲偡偲尒塰偊傕僗僢僉儕偟傑偡丅

Z-293丂僼儔僢僋僗儕儉乕僶丄丂Z-76丂僋儕乕儞億僢僩乮儂乕僓儞乯乮堦椺乯傕曋棙偱偡丅

桘惈僒僀儞儁儞偺僀儞僋傕棊偲偣傞偺偱尋媶奐敪梡婎斅偺儊儌棑偺彂偒姺偊偵傕曋棙偱偡丅

|

|

儕乕僪晹昳偺晍儅僢僩

|

儕乕僪晹昳偺敿揷晅偗丄摿偵攚偺崅偄晹昳傪庢傝晅偗偨屻偺攚偺掅偄儕乕僪晹昳偼晹昳偑壓曽偵扙棊偡傞偺偱敿揷晅偗偑偟擄偄傕偺偱偡丅

偦偺條側応崌偼丄侾俆俠倣妏掱搙偺栘柸偺晍傪儅僢僩忬偵愜傝偨偨傫偱晹昳偵摉偰偰偐傜丄婎斅傪斀揮偝偣偰嶌嬈戜偵抲偔偲晹昳偺扙棊偑杊偘傑偡丅

偙偺帪丄嶌嬈戜偐傜婎斅乮偺巟帩梡巟拰乯偑彮偟晜偔掱搙偺儅僢僩岤偵偡傞偺偑億僀儞僩偱偡丅

屻偼婎斅傪忋偐傜墴偟晅偗側偑傜敿揷晅偗傪偟傑偡丅

廮傜偐傔偺俬俠梡摫揹儅僢僩傪彫偝偔愗偭偰巊梡偡傞帠傕偱偒傑偡偑丄壛擬偱曄宍偡傞帠傕偝傞帠側偑傜丄堎廘乮桳撆僈僗丠乯偑敪惗偡傞偺偱彠傔傜傟傑偣傫丅

丂 丂

丂 丂

丂 丂

丂 丂

|

|

儅僗僉儞僌僥乕僾偺棙梡

|

尋媶奐敪梡婎斅偱偼昞柺幚憰晹昳偺抂巕偵偼攝慄偺堊偵昁偢偦偺嬤朤偵僷僞乕儞偱愙懕偟偨僗儖乕儂乕儖傪愝偗偰偄傑偡丅

昞柺幚憰晹昳偺敿揷晅偗偺嵺偵僗儖乕儂乕儖偵敿揷偑棳傟崬傒擄偔偡傞條側宍忬偺敿揷儗僕僗僩偵偟偰偄傑偡偑丄敿揷晅偗媄弍偵晧偆柺傕桳傝姰慡偱偼偁傝傑偣傫丅

晄梫売強傊偺敿揷杊巭偵偼懴擬惈僋儗乕僾儅僗僉儞僌僥乕僾乮廧桭俁俵乯乮堦椺乯偺條側儅僗僉儞僌僥乕僾偑曋棙偱偡丅

庤敿揷嶌嬈偱偼彮検偺僥乕僾傪攳偑偟偰巊偄夞偣傞偺偱柍帇偱偒傞掱偺僐僗僩偱嵪傒傑偡丅

傑偨丄敿揷晅偗晹偵椬愙偟偰婛偵幚憰偟敿揷晅偗偝傟偨晹昳偑桳偭偨応崌偵丄偙傟傪儅僗僉儞僌僥乕僾偱

僇僶乕偡傞帠偵傛傝丄敿揷僑僥偑柍梡偵愙怗偟偰偦偺敿揷晅偗傪懯栚偵偡傞帠偐傜曐岇偱偒傞偲偄偆傕偆堦偮偺儊儕僢僩偑桳傝傑偡丅

|

|

僠僢僾晹昳偺抂巕忲敪

|

僲乕僽儔儞僪昳偺僠僢僾掞峈偵偼丄抂巕偑擬偵庛偔丄堦斒揑悇彠壏搙乮俁俁侽乣俁係侽亷丄墧僼儕乕乯偱傕抂巕偵捈愙敿揷僐僥愭傪摉偰傞偲捈偪偵抂巕偑忲敪偟偰偟傑偆暔偑桳傝傑偟偨丅

偦偺條側応崌偼僷僢僪偺晹昳抂巕嬤朤傪敿揷僐僥愭偱壛擬偟偰偦偙偐傜僴儞僟偑晹昳抂巕偵棳傟崬傫偱峴偔條偵偡傞偺偑椙偔丄抂巕偑忲敪偟側偄暔偱偁傟偽擮偺堊嵟屻偵扨帪娫抂巕偵敿揷僑僥傪愙怗偝偣傞偲椙偄條偱偡丅

偟偐偟丄偦偺條側晹昳偼嵟弶偐傜巊梡偟側偄偵墇偟偨帠偼偁傝傑偣傫丅

亂曗懌亃婔偮偐偺擔杮儊乕僇偺僽儔儞僪昳傪帋偟偨張丄栤戣偲側傞條側暔偼桳傝傑偣傫偱偟偨丅

丂乮夵掶 2018/07/21乯

|

| 崁丂丂丂丂栚 |

婰丂丂丂丂丂丂丂帠 |

|

墳梡夞楬

|

媄弍帒椏偵傕懡悢桳傝丅

|

|

揹尮嫙媼僐僱僋僞

|

尋媶奐敪梡婎斅傊偺揹尮嫙媼僐僱僋僞偼偦偺僺儞傾僒僀儞傕娷傔忢偵摨堦偵偟偰抲偒傑偟傚偆丅

揹尮憰抲偐傜偺揹尮嫙媼働乕僽儖傪偦偺搒搙嶌惉偣偢丄愙懕曄峏傕偣偢偵巊偄夞偣傑偡丅

乮働乕僽儖惢嶌傗働乕僽儖愙懕嶌嬈偼寢峔柺搢偱妝偟偔傕偁傝傑偣傫乯

|

|

僱僕巭傔幃揹尮僐僱僋僞

|

揹尮嫙媼僐僱僋僞傪帺桼偵慖戰偱偒傞応崌偼丄愱梡偺埑拝岺嬶偑晄梫側僱僕巭傔幃偑偍彠傔偱偡丅

椺偊偽MC 1,5/N-ST-3,81 Phoenix Contact 乮堦椺乯偑桳傝傑偡丅

乮Phoenix Contact幮偺儂乕儉儁乕僕丄僇僞儘僌偼旕忢偵暘偐傝擄偄偺偱丄擖庤惈偺揰偐傜傕儕儞僋愭偼忋婰偲偟傑偟偨丅乯

僺僢僠俁丏俉侾倣倣側偺偱戝宎儕乕僪梡儐僯僶乕僒儖婎斅俹倃侾俀俀侽丄俠俫俬俹乛俢俬俹寭梡儀乕僗儐僯僶乕僒儖婎斅 俹倃侾俁侾侽偱偼捛壛岺柍偟偱婎斅懁僐僱僋僞傪捈愙幚憰偱偒傑偡丅

丂 丂

|

|

儊儌棑偺妶梡

|

尋媶奐敪梡婎斅偵偼夞楬偺巊偄夞偟偑偱偒傞棙揰傕偁傝傑偡丅

偦偺堊偵偼娗棟曽朄偑戝帠偱丄惢嶌戜悢偑憹偊偰偔傞偲幚婡傪曐娗偟偰抲偄偰傕壗偺夞楬偐敾傜側偔側偭偰偟傑偆條偱偼扅偺僑儈偵側偭偰偟傑偄傑偡丅

尋媶奐敪梡婎斅偵偼僔儖僋偵傛傞懡偔偺儊儌棑偑桳傞偺偱丄偙偙偵夞楬恾斣崋傗夞楬柤摍娗棟偵昁梫側帠暱傪彂偒崬傫偱抲偔偲帪娫偑宱偭偰傕栤戣側偔嵞棙梡偑偱偒傑偡丅

峔憿揑偵偼夞楬偺夵憿傕梕堈偵峴側偊傑偡偺偱丄偦偺応崌偵偼夞楬恾偺曄峏傕惓妋偵巆偟偰抲偒傑偡丅

丂 丂

|

|

戝梕検僷僗僐儞偺梫斲

|

杦偳偺尋媶奐敪梡婎斅偺揹尮擖椡晹偵偼侾俇侽俉僒僀僘偺僠僢僾僐儞僨儞僒埲奜偵嵟掅冇俇丏係倣倣偺揹夝僐儞僨儞僒

枖偼俆俈俆侽僒僀僘枠偺僠僢僾僐儞僨儞僒偑幚憰偱偒傞條偵偟偰偄傑偡

婎斅扨懱偱巊梡偡傞応崌偼偦偺僼僢僩僾儕儞僩偵崌偆斖埻偱戝偒傔偺梕検偺僐儞僨儞僒傪幚憰偟偰偍偗偽埨怱偱偡丅

偟偐偟丄暋悢婎斅傪楢寢巊梡偟偨傝丄俠俫俬俹乛俢俬俹寭梡儀乕僗儐僯僶乕僒儖婎斅俹倃侾俁侾侽偺僪乕僞儃乕僪偲偟偰

幚憰偡傞応崌偼丄揹尮嫙媼晹偵戙昞偱戝梕検僐儞僨儞僒傪幚憰偡傟偽丄慡偰偺婎斅偵戝梕検僐儞僨儞僒傪愝偗傞昁梫偼桳傝傑偣傫丅

椺偊偽屻幰偺応崌偵偼僪乕僞儃乕僪偼侾俇侽俉偺侽丏侾兪俥僠僢僾僐儞僨儞僒偩偗偱栤戣柍偟偺幚愌偑桳傝傑偡丅

|

|

倁俿僷僞乕儞

|

丂僔儞僌儖僆儁傾儞僾婎斅俹倃侾俁俁侽偵偼倁俿僷僞乕儞偑桳傝傑偡丅

丂僔儞僌儖僆儁傾儞僾婎斅俹倃侾俁俁侽偵偼倁俿僷僞乕儞偑桳傝傑偡丅

丂偙傟偼僺儞僿僢僟傗庬乆偺僺儞攝抲偺壜曄掞峈丄僩儔儞僕僗僞丄僟僀僆乕僪偑俁抂巕俽俷俿傕娷傔丄儕乕僪晹昳丄昞柺幚憰晹昳偵娭傢傜偢幚憰偱偒傞條偵偟偨暰幮僆儕僕僫儖偺僼僢僩僾儕儞僩偱偡丅

丂偙傟偵傛傝丄僩儔儞僕僗僞夞楬丄僎僀儞挷惍夞楬丄僆僼僙僢僩挷惍夞楬丄婎弨揹埑嶌惉夞楬丄僕儍儞僷僐僱僋僞偵傛傞慖戰夞楬摍懡條側夞楬偑彮側偄攝慄偱慻傔傑偡偺偱丄夞楬愝寁帪偵偼桳岠棙梡偟偰壓偝偄丅

丂 丂

|

|

僷僢僪僀儞DIP

|

尋媶奐敪梡婎斅偺懡偔偵偼嬻偒僗儁乕僗偵儐僯僶乕僒儖僄儕傾偲偟偰暰幮僆儕僕僫儖偺僷僢僪僀儞俢俬俹僷僞乕儞傪愝偗偰偄傑偡丅

偙傟偼俀屄埗楢寢偟偨俀丏俆係倣倣僺僢僠偱攝抲偟偨僗儖乕儂乕儖偺娫偵僠僢僾晹昳傑偨偼俁抂巕俽俷俿偺昞柺幚憰晹昳梡僷僢僪傪攝抲偟丄

昞柺幚憰晹昳傊偺攝慄偼僗儖乕儂乕儖傪夘偟偰峴側偆條偵偟偨傕偺偱丄

昞柺幚憰晹昳傪幚憰偟側偄応崌偼捠忢偺俀楢僗儖乕儂乕儖偺儐僯僶乕僒儖婎斅偲摨條偵埖偊傑偡丅

愱梡偺僺僢僠曄姺婎斅傪巊梡偣偢偵昞柺幚憰晹昳傪巊偊丄夞楬愝寁偺僼儗僉僔價儕僥傿偑戝暆偵憹壛偟傑偡丅

丂 丂

|

|

揹尮僌儔儞僪偲僔僌僫儖僌儔儞僪偺愙懕

|

尋媶奐敪梡婎斅偱偼揹尮僌儔儞僪乮俧俶俢乯偲僔僌僫儖僌儔儞僪乮俽俧乯傪暘棧偟偰僌儔儞僪宯摑偺攝慄偵僼儗僉僔價儕僥傿傪帩偨偣偰偄傑偡丅

幚嵺偺夞楬偱偼偙傟傜傪壗張偐堦揰偱愙懕偡傞昁梫偑桳傝傑偡丅

戝尦偺揹尮晹偱偺抁棈丄婎斅扨懱偱巊梡偡傞応崌偼偦偺婎斅忋偺愙懕僕儍儞僷傪抁棈丄暋悢慻傒崌傢偣傞応崌偼壗傟偐侾戜偺婎斅偺愙懕僕儍儞僷傪抁棈丄偺曽朄偑桳傝傑偡丅

俠俫俬俹乛俢俬俹寭梡儀乕僗儐僯僶乕僒儖婎斅俹倃侾俁侾侽傪巊梡偡傞応崌偼戝尦偺揹尮晹偐俹倃侾俁侾侽忋偺揹尮嫙媼晹偱抁棈偟丄奺僪乕僞儃乕僪偺愙懕僕儍儞僷偼僆乕僾儞偺傑傑偲偟傑偡丅

僆乕僾儞乛僔儑乕僩傪曄峏偡傞壜擻惈偑偁傞応崌偼丄偦偺僕儍儞僷慄幚憰晹偵俀嬌僺儞僿僢僟僐僱僋僞傪幚憰偟偰偍偔偲梕堈偵曄峏偱偒偰曋棙偱偡丅

|

昞柺幚憰偼傫偩晅偗梡僣乕儖乽SMD僋儔儞僾乿乿偼昞柺幚憰晹昳偺偼傫偩晅偗偵戝曄曋棙偱偡丅

昞柺幚憰偼傫偩晅偗梡僣乕儖乽SMD僋儔儞僾乿乿偼昞柺幚憰晹昳偺偼傫偩晅偗偵戝曄曋棙偱偡丅

丂

丂

丂

丂 丂

丂

丂婎斅偵崌傢偣偨愨墢梡掙斅傪丄梊傔傑偲傔偰惢嶌偟偰偍偔偲曋棙偱偡丅

丂婎斅偵崌傢偣偨愨墢梡掙斅傪丄梊傔傑偲傔偰惢嶌偟偰偍偔偲曋棙偱偡丅

丂

丂

丂

丂

丂

丂

丂

丂