FPGAのテスト容易性向上

チェック用信号をユニバーサル・コネクタエクステンダで観測

(リンク元:「技術資料」)

●FPGA内の信号観測

FPGAやCPLD(以下FPGAで統一)を用いた回路では、何らかのトラブルが発生した場合、内部の信号を観測したい場合があります。

FPGAやCPLD(以下FPGAで統一)を用いた回路では、何らかのトラブルが発生した場合、内部の信号を観測したい場合があります。

特に外部信号の関係が複雑に絡み合う場合のトラブルシュートではそうです。

JTAG等で内部信号を観測するツールもある様ですが、コスト高や使いこなす迄の手間がネックとなり、導入には敷居が低いとは言い難いものです。

そこで一般的には、観測したい信号をFPGAの不使用ピンに接続し、シンクロスコープやロジックアナライザで観測します。

この方法は手っ取り早く、直感的で手軽です。

しかし、狭ピッチのQFPや、BGAのFPGAではプロービングは一苦労で、その上PCIバスの様に何らかのバス用シャーシに実装されたり、ボードを重ねて実装するスタック構造の場合の下側のボードではプロービングは困難です。

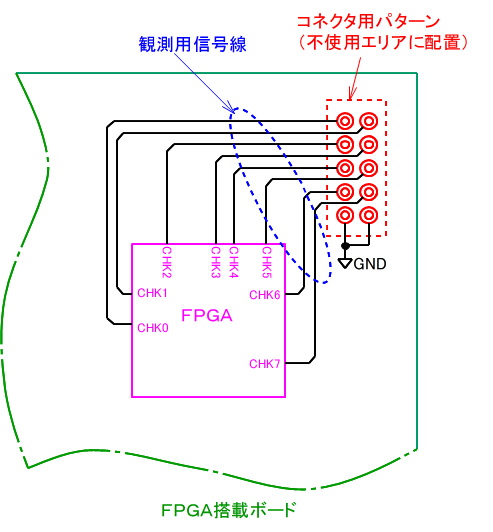

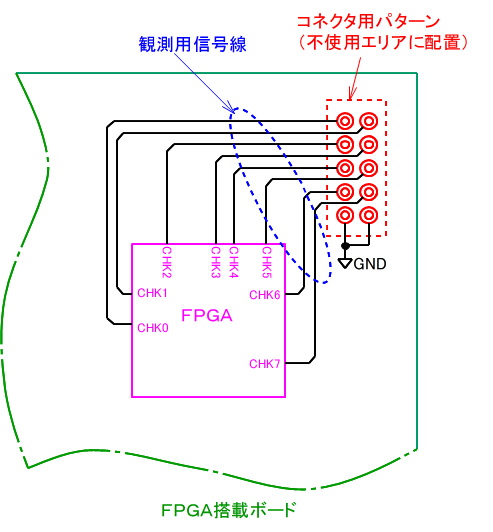

その様な場合には、ボード設計の段階で予めFPGAの不使用ピンを観測用の出力端子として用意して置き、

他の回路の邪魔にならないデッドスペースに2.54mmピッチ2列ピンヘッダ相当のコネクタ用パターンに引き出して置くと便利です。

FPGAから観測用信号線を引き出す

(クリックで拡大)

|

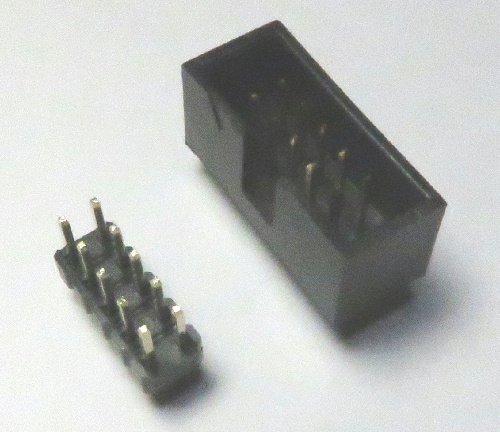

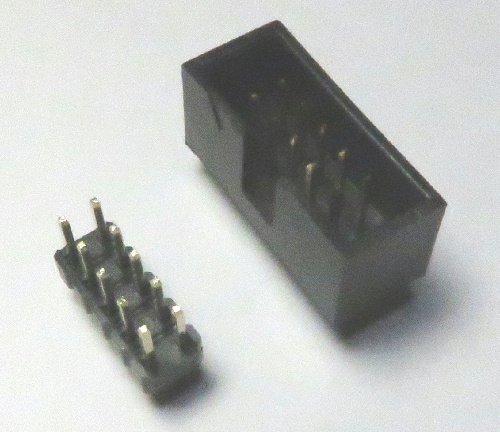

コネクタ(ピンヘッダ)の例

(クリックで拡大)

|

コネクタ(ピンヘッダ)は通常は不実装とし、信号の観測が必要になった場合に実装するのでも構いません。

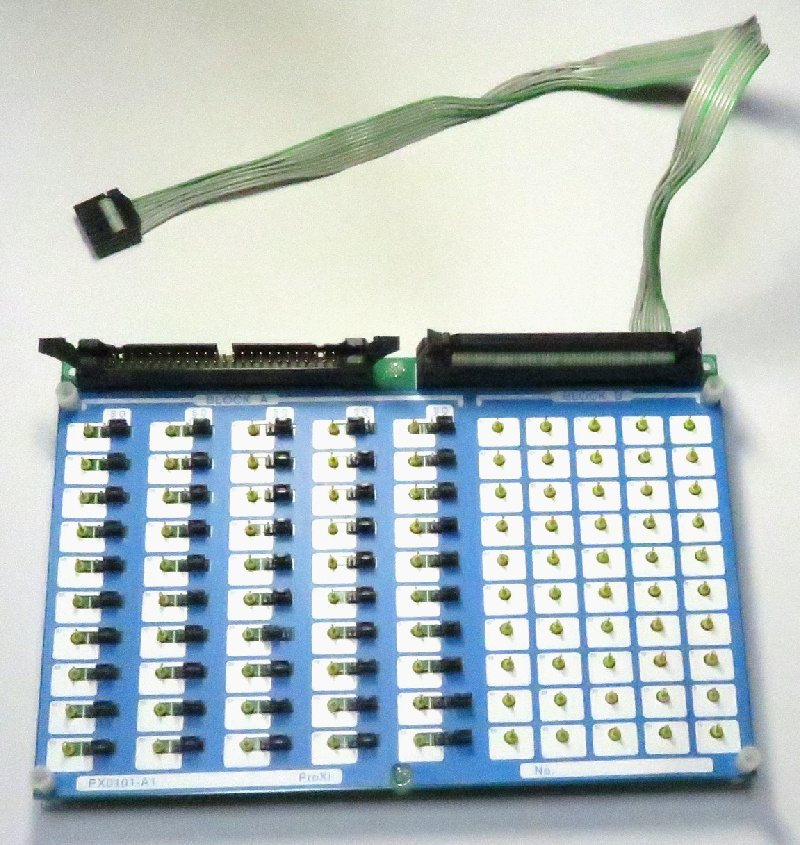

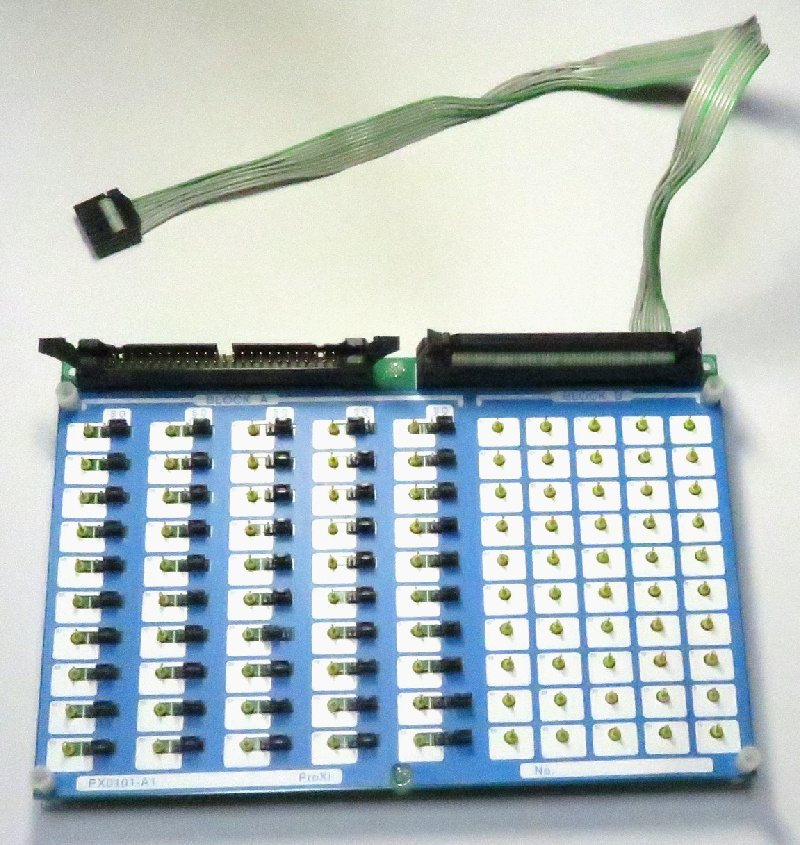

そのコネクタに適合するケーブルでユニバーサル・コネクタエクステンダ PX0101に接続し、PX0101上のチェックピンに測定器のプローブを接続します。

観測したい信号を観測用出力端子に接続する様にFPGAのプログラムデータを変更すれば、任意の信号を容易にチェックピンに引き出せます。

これにより、大きなコストを掛けずにFPGAのパッケージ形状や、ボードの実装位置に関わらず、内部信号を容易に観測できる様になり、

FPGAのテスト容易性が大幅に向上します。

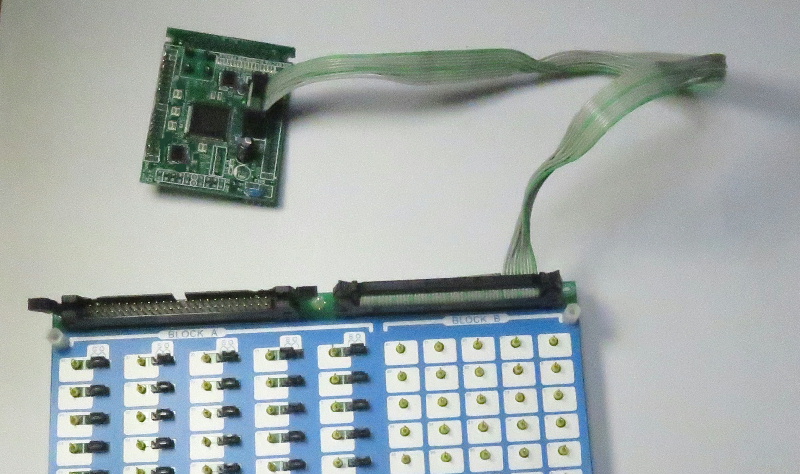

信号引き出し用ケーブルを接続した

ユニバーサル・コネクタエクステンダ PX0101

(クリックで拡大)

|

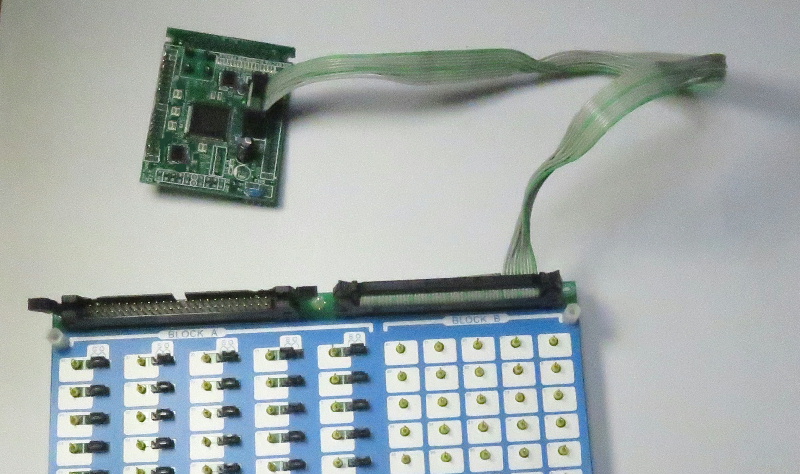

使用状態のイメージ

(クリックで拡大)

|

(初版 2018/09/29)

(リンク元:「技術資料」)

−−−−− 本ページはここまで −−−−−

FPGAやCPLD(以下FPGAで統一)を用いた回路では、何らかのトラブルが発生した場合、内部の信号を観測したい場合があります。

FPGAやCPLD(以下FPGAで統一)を用いた回路では、何らかのトラブルが発生した場合、内部の信号を観測したい場合があります。