PCI�o�X�����e�X�g�x���`�p�T�u�v���O����

PCI�o�X�^�[�Q�b�g�p�e�X�g�x���`���ȒP�ɍ쐬����

�P�D�͂��߂�

�@PCI�o�X�� 2002�N������ PCI Express�o�X�ɒu����������l�ɂȂ�A�ߔN�͗]��g�p����Ȃ��Ȃ����l�ł��A���i��������r�I�����Y�Ɨp�V�X�e���ł͌���ł������ł��B

�@PCI�o�X�� 2002�N������ PCI Express�o�X�ɒu����������l�ɂȂ�A�ߔN�͗]��g�p����Ȃ��Ȃ����l�ł��A���i��������r�I�����Y�Ɨp�V�X�e���ł͌���ł������ł��B

�@�������Z�p�e�[�}�Ƃ��Ă͌Â��ׂ��A�l�b�g�ł̏��͖R������ۂł��B

�@�Ⴆ�APCI�o�X�pIP��FPGA�ɍڂ���PCI�o�X�p�^�[�Q�b�g�f�o�C�X�삷��ۂ̃e�X�g�x���`���ȒP�ɍ쐬�ł���l�ȃ��C�u�������l�b�g�ŒT���Ă�������܂���ł����B

�@IP���[�J����ɂ͂���̂ł��傤���A����̓T�|�[�g���Ă��Ȃ����A�L��PCI-IP�̐������[�U�����T�|�[�g����Ȃ��͗l�ł��B

�@������PCI�o�X�^�[�Q�b�g�p�e�X�g�x���`�̃��C�u�������쐬���܂����B

�@PCI�o�X�̌���ł͎g�p����@��͂��������͂Ȃ������ł����A�F���ł��Ȃ������Ȃ̂ŁA�@�����Η��p���Ă݂ĉ������B

�@�Ȃ��A�\�[�X�̉������͍\���܂��A�{�e�̃I���W�i���\�[�X�Ɋւ��Ă͕��Ђɒ��쌠��������̂Ƃ��A�����p�̍ۂ͂��̎|���L�ڂ��ĉ������B

�@�܂����ʂɂ��Ă̐ӔC�Ђ͕����܂���̂ŁA�����p�͎��ȐӔC�ōs�Ȃ��ĉ������B

�@�Y�t����\�[�X�t�@�C����ASIAN�L�@�iHDL�ɂ�����M�����̌�����@�j�ɂ��܂��B

�@�Ȃ��A�{�e��PCI�o�X��ModelSim�ɂ��Ă̒m����L���Ă��鎖��O��Ƃ��A�ڍא����͏Ȃ��܂��B

�Q�DPCI�o�X���C�u�����g�p��

�@PCI�o�X�̗��p�҂ł�����C�u�����̎g�p���@�́A�ׂ����������g�p�������̂��ł������Ɖ��p�����Ղ��Ǝv����̂ŁA

�����ł͊�{�I�ŊȒP�Ȏg�p����L���ă��[�U�[�Y�}�j���A���̑�ւ��Ƃ��܂��B

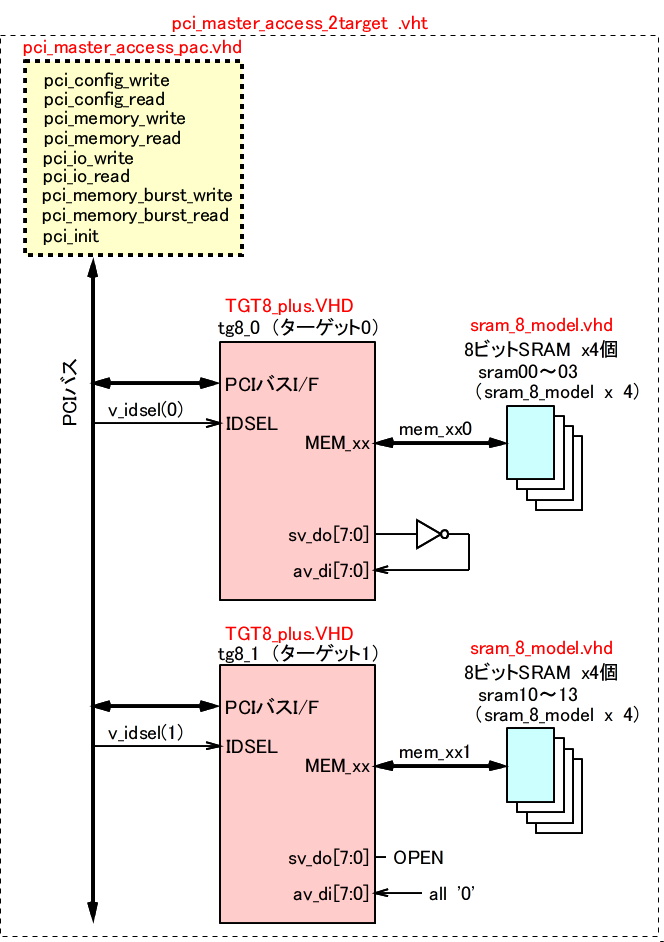

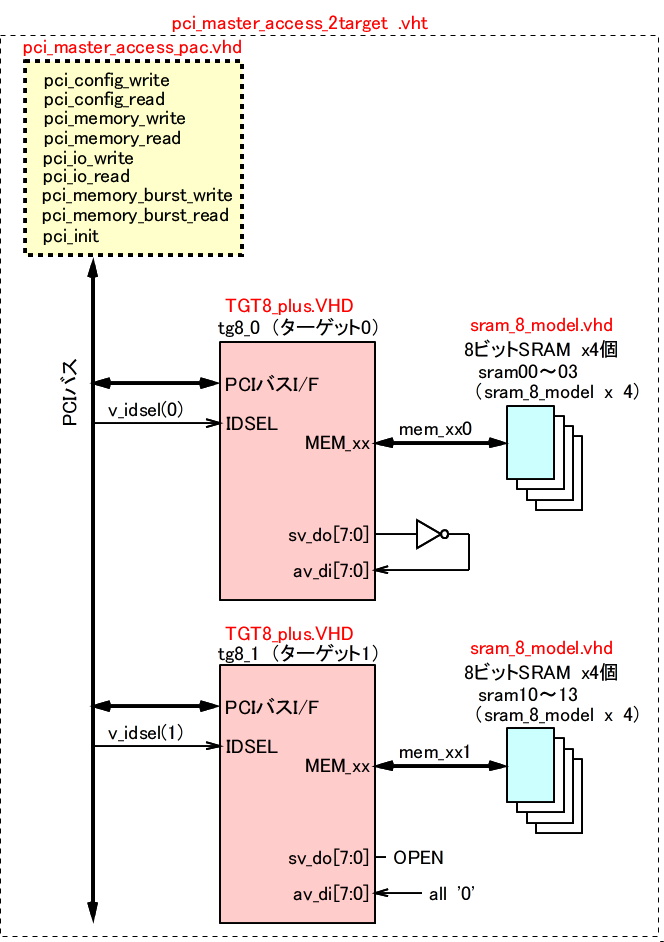

���V�X�e���\��

�@�}1�Ƀe�X�g�x���`�̃V�X�e���\���������܂��B

�i�N���b�N�Ŋg��j

�@�@�@�}�P�D�e�X�g�x���`�̃V�X�e���\���@

���g�p�t�@�C��

| �t�@�C���� |

�t�@�C�����e |

pci_master_access_2target.vht

|

�e�X�g�x���`�{��

�^�[�Q�b�g�̃R���t�B�M�����[�V�����ASRAM�̃��C�g/���[�h�AI/O���C�g�^���[�h���s�Ȃ��B

IDSEL�̎g�p���@�Ƌ@�\��Ղ�����ׂɃ^�[�Q�b�g��2�̃V�X�e���ɂ����B

|

pci_master_access_pac.vhd

|

�e�X�g�x���`�p���C�u����

���̒��� pci_config_write ���e��T�u�v���O�������e�X�g�x���`���ɋL�q���鎖�ŁAPCI�o�X�����B

|

TGT8_plus.VHD

|

�e�X�g�x���`�p���C�u�����̓�����m�F����ׂ̃^�[�Q�b�g�pPCI-IP

���[�U�p�e�X�g�x���`���쐬����ۂɂ͖{IP�����[�U�g�p��PCI-IP�ɒu��������B

�ȉ��̃\�[�X�t�@�C�����ꕔ�ҏW��������

Interface���� TECH I Vol.3�@PCI�f�o�C�X�v���� �iCQ�o�Łj�@�t��CD�� VHDL�\�[�X

�^�[�Q�b�g8 (�o�[�X�g�]���Ή�) TGT8.VHD

���쌠�ҁF���{��q�v ��

�ҏW�҂ɂ��ύX�ӏ��� �u--px0�v��t�L�B

��ȕύX�͈ȉ��̒ʂ�B

�@DI�ADO�@�e8�_����I/O���W�X�^�lj��B

�@�x�[�X�A�h���X +4 �Ԓn�FDO[7..0] WR/RD

�@�x�[�X�A�h���X +6 �Ԓn�FDI[7..0] RD ONLY

�A��M�f�[�^�̃p���e�B�`�F�b�N��lj��B

�@�p���e�B�G���[���� PERR_n ��'0'�ɂ���B

�@PERR_n �͎�M���삪�I�������玩���N���A�����B

|

sram_8_model.vhd

|

�e�X�g�x���`�p8�r�b�gSRM���f��

SRAM�̃A�h���X���� RAM_ADR_WIDTH �Œ�`���邪�A�g�p����p�\�R���̊��i�������ʁj�ɂ���Ă̓R���p�C�����Ƀp�\�R�����n���O����B

pci_master_access_2target.vht �ł� Note1 �̉ӏ��ňȉ��̗l��'10'�ɂ��Ă��邪�A�p�\�R�����ɂ���Ă͂���ɏ������l�ɂ��Ȃ���Ȃ�Ȃ���������Ȃ��B

�@constant SET_RAM_ADR_WIDTH : integer := 10;�@�@�@-- sram address bit

|

���k�t�@�C���ꎮ

rtl_pci_test_bench.zip

|

��L�̑S�t�@�C���ꎮ���ꊇ���Ĉ��k��������

�_�E�����[�h���ĉ𓀂���\�[�X�t�@�C���Ƃ��ė��p�\�B

|

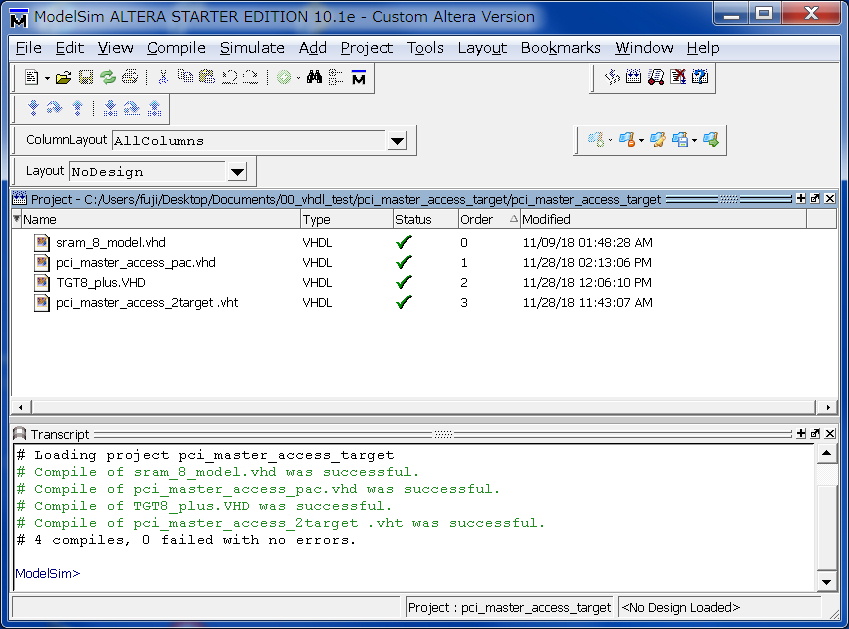

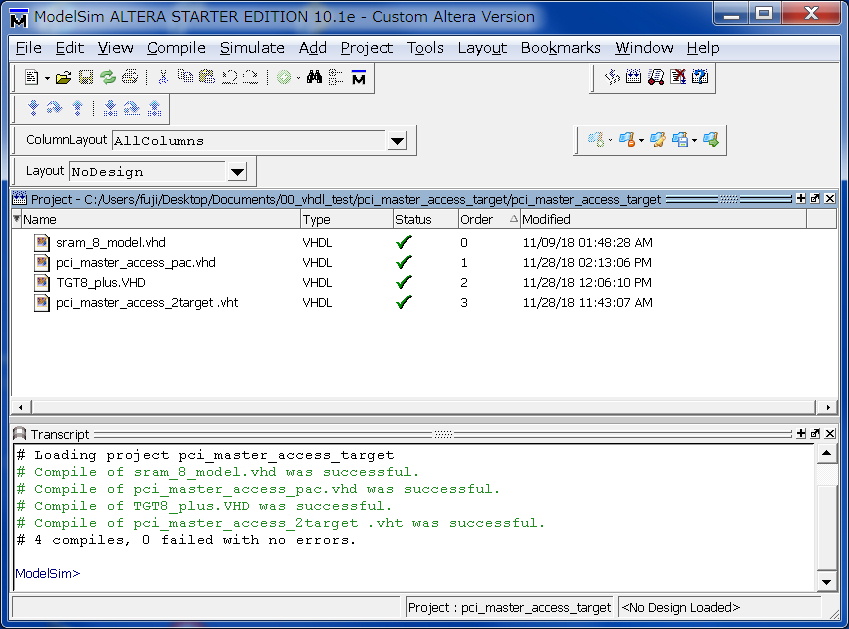

��ModelSim���

�@�}�Q�́A ModelSim ALTERA STARTER EDITION 10.1e Revision: 2013.06 (ALTERA)�̃v���W�F�N�g��ʂł��B

�@�}�Q�́A ModelSim ALTERA STARTER EDITION 10.1e Revision: 2013.06 (ALTERA)�̃v���W�F�N�g��ʂł��B

�i�N���b�N�Ŋg��j

�}�Q�DModelSim ALTERA STARTER EDITION�̃v���W�F�N�g���

���V�~�����[�V��������

�@�}�R�́A ModelSim ALTERA STARTER EDITION 10.1e Revision: 2013.06 (ALTERA)�ɂ��V�~�����[�V�������ʂł��B

�i�N���b�N�Ŋg��j

�i�N���b�N�Ŋg��j

�@�@�@�@�@�}�R�D�V�~�����[�V��������

�����p���@

�@�ȉ��̎菇�Ŕ�r�I�e�ՂɃ��[�U��PCI�o�X�𐧌�ł��܂��B

�@�ȉ��̎菇�Ŕ�r�I�e�ՂɃ��[�U��PCI�o�X�𐧌�ł��܂��B

�@���k�t�@�C���ꎮ���_�E�����[�h����B

�ATGT8_plus.VHD�����[�U�g�p��PCI-IP�ɒu��������

�Bpci_master_access_2target.vht�@�����[�U�V�X�e���p�e�X�g�x���`�ɉ�������B

�@���̒��� pci_master_access_pac.vhd ���ȉ��̗l�Ƀp�b�P�[�W�錾����B

�@�@use work.pci_master_access_pac.all;

�Cpci_master_access_2target.vht ���̃T�u�v���O�����g�p�������R�s�[���ăJ�X�^�}�C�Y����B

���Q�l����

�@PCI�o�X�e�X�g�x���`�쐬�ɓ�����A�ȉ��̎������Q�l�ɂ��܂����B

�@OPEN DESIGN No.7�@PCI�o�X�̏ڍׂƉ��p�ւ̃X�e�b�v�@�iCQ�o�ŎЁj

�AC&E TUTORIAL�@VHDL�ɂ��n�[�h�E�F�A�v����i���Łj�@���J��T���@�iCQ�o�ŎЁj

�BTECHI Vol.3�@�C���[�t�F�C�X�����@PCI�f�o�C�X�v����@�i���Łj�iCQ�o�ŎЁj

***********************************************

�@�{�e�̎��ł���uPCI�o�X�^�[�Q�b�g�p�e�X�g�x���`�v�̍쐬���@�͈ȏ�ł��B

�@�ȉ��͕⑫�����Ƃ��Ċ֘A�������L�ڂ������̂Ȃ̂ŁA���������������������炲���������B

�y�⑫�����z

���T�u�v���O�����̉���

���T�u�v���O�����̉���

�@PCI�o�X�p�e�X�g�x���`�̖ړI�͈ȉ���2�ł��B

�@�g�p����PCI-IP�̓���m�F

�@�e��^�C�~���O�ύX�A�p���e�B�G���[�����A32�r�b�g�o�E���_���ȊO�̃A�h���X�ł̃A�N�Z�X���A

PCI�o�X�̐���A�N�Z�X�ȊO�̃C���[�K���ȃA�N�Z�X���K�v�B

�APCI-IP�̓���͐���ł���A�����p�����^�[�Q�b�g�̓���m�F

�@PCI�o�X�͐���A�N�Z�X�����邾���ŗǂ��A�p���e�B�G���[���͔���������K�v�͂Ȃ��B

�@�{�e��PCI�o�X�����e�X�g�x���`�p�T�u�v���O�����͇@�A�A�̉���ɂ��e�ՂɑΉ��ł��܂��B

�@���邢�̓p���e�B�G���[��������菜�����ŁA�e�ՂɇA��p�̐ݒ�v�f�����Ȃ��T�u�v���O�����ɉ������鎖���ł��܂��B

�@�܂��A�o�[�X�g�]�����̍ő�f�[�^���𑝂₷���� pci_master_access_pac.vhd ��

�@constant MAX_DATA�@�@: integer := 4;

�̒l�ƁA�֘A����s���ύX���鎖�ŗe�Ղɂł��܂��B

�@����ɁA��ʂ̃f�[�^�����C�g�^���[�h����ꍇ�ɕ֗��ȁA�f�[�^�t�@�C����p�����e�X�g�x���`�ւ̉�������r�I�e�Ղɂł��܂��B

���T�u�v���O�����̐���

�@�e�T�u�v���O������ procedure �Ƃ��Ă���̂ŁA���v�̏����Z�b�g���ăe�X�g�x���`���ɖ��ߍ��ނ�����PCI�o�X���ȒP�ɐ���ł��܂��B

�i�P�j�R���t�B�M�����[�V�����E���C�g�@pci_config_write

procedure pci_config_write (

set_dev_no : in integer range 0 to 31; -- --px1

set_address : in std_logic_vector(31 downto 0); --

set_ad_perr : in std_logic; -- 1: ng_parity, 0: ok_parity

set_wr_data : in std_logic_vector(31 downto 0); --

set_be_n : in std_logic_vector(3 downto 0); --

set_data_perr : in std_logic; -- 1: ng_parity, 0: ok_parity

----

signal clk : in std_logic; --

signal trdy_n : in std_logic; --

signal devsel_n : in std_logic; --

signal v_idsel : out std_logic_vector(31 downto 0); --

signal frame_n : out std_logic; --

signal ad : inout std_logic_vector(31 downto 0); --

signal c_be_n : out std_logic_vector(3 downto 0); --

signal irdy_n : out std_logic; --

signal par : inout std_logic --

);

| �ݒ荀�� |

�ݒ���e |

set_dev_no

|

integer range 0 to 31

�R���t�B�M�����[�V�����Ώۂ̃^�[�Q�b�g��I������M���� IDSEL�𐮐� 0 �` 31�Ŏw��B

|

set_address

|

std_logic_vector(31 downto 0)

���C�g�Ώۂ̃A�h���X���w��B

|

set_ad_perr

|

std_logic

�A�h���X�ɑ���p���e�B�G���[��ݒ�B

�p���e�B�� PAR �� ����p���e�B�iOK�j�ɂ��邩�G���[�p���e�B�iNG�j�ɂ��邩��I������B

0�FOK�A�@1�FNG

|

set_wr_data

|

std_logic_vector(31 downto 0)

���C�g����f�[�^��ݒ�B

|

set_be_n

|

std_logic_vector(3 downto 0)

���C�g�f�[�^�ɑ��� C/BE[3:0]# �M���̃o�C�g�C�l�[�u���M�� be_n �̒l��ݒ�B

|

|

set_data_perr

|

std_logic

���C�g�f�[�^�ɑ���p���e�B�G���[��ݒ�B

�p���e�B�� PAR �� ����p���e�B�iOK�j�ɂ��邩�G���[�p���e�B�iNG�j�ɂ��邩��I������B

0�FOK�A�@1�FNG

|

|

���̑��̐M��

|

clk �ȉ��̐M���͖{procedure �ƊO���M����ڑ�����ׂ̂��́B

���[�U�̕ҏW�֎~�B

|

�i�Q�j�R���t�B�M�����[�V�����E���[�h�@pci_config_read

procedure pci_config_read (

set_dev_no : in integer range 0 to 31; -- --px1

set_address : in std_logic_vector(31 downto 0); --

set_ad_perr : in std_logic; -- 1: ng_parity, 0: ok_parity

set_be_n : in std_logic_vector(3 downto 0); --

----

signal clk : in std_logic; --

signal trdy_n : in std_logic; --

signal devsel_n : in std_logic; --

signal v_idsel : out std_logic_vector(31 downto 0); --

signal frame_n : out std_logic; --

signal ad : inout std_logic_vector(31 downto 0); --

signal c_be_n : out std_logic_vector(3 downto 0); --

signal irdy_n : out std_logic; --

signal par : inout std_logic; --

signal perr_n : out std_logic; --

signal sv_read_data : out std_logic_vector(31 downto 0) -- for test

);

| �ݒ荀�� |

�ݒ���e |

set_dev_no

|

integer range 0 to 31

�R���t�B�M�����[�V�����Ώۂ̃^�[�Q�b�g��I������M���� IDSEL�𐮐� 0 �` 31�Ŏw��B

|

set_address

|

std_logic_vector(31 downto 0)

���[�h�Ώۂ̃A�h���X���w��B

|

set_ad_perr

|

std_logic

�A�h���X�ɑ���p���e�B�G���[��ݒ�B

�p���e�B�� PAR �� ����p���e�B�iOK�j�ɂ��邩�G���[�p���e�B�iNG�j�ɂ��邩��I������B

0�FOK�A�@1�FNG

|

set_be_n

|

std_logic_vector(3 downto 0)

���[�h�f�[�^�ɑ��� C/BE[3:0]# �M���̃o�C�g�C�l�[�u���M�� be_n �̒l��ݒ�B

|

|

���̑��̐M��

|

clk �ȉ��̐M���͖{procedure �ƊO���M����ڑ�����ׂ̂��́B

���[�U�̕ҏW�֎~�B

�Ȃ��Asv_read_data �̓��[�h�����f�[�^��Ղ��l�Ƃ��Ĕg�`�\������ׂ̂��̂ł���B

|

�i�R�j�������E���C�g�@pci_memory_write

procedure pci_memory_write (

set_address : in std_logic_vector(31 downto 0); --

set_ad_perr : in std_logic; -- 1: ng_parity, 0: ok_parity

set_wr_data : in std_logic_vector(31 downto 0); --

set_be_n : in std_logic_vector(3 downto 0); --

set_data_perr : in std_logic; -- 1: ng_parity, 0: ok_parity

----

signal clk : in std_logic; --

signal trdy_n : in std_logic; --

signal devsel_n : in std_logic; --

signal frame_n : out std_logic; --

signal ad : inout std_logic_vector(31 downto 0); --

signal c_be_n : out std_logic_vector(3 downto 0); --

signal irdy_n : out std_logic; --

signal par : inout std_logic --

);

| �ݒ荀�� |

�ݒ���e |

set_address

|

std_logic_vector(31 downto 0)

���C�g�Ώۂ̃A�h���X���w��B

|

set_ad_perr

|

std_logic

�A�h���X�ɑ���p���e�B�G���[��ݒ�B

�p���e�B�� PAR �� ����p���e�B�iOK�j�ɂ��邩�G���[�p���e�B�iNG�j�ɂ��邩��I������B

0�FOK�A�@1�FNG

|

set_wr_data

|

std_logic_vector(31 downto 0)

���C�g����f�[�^��ݒ�B

|

set_be_n

|

std_logic_vector(3 downto 0)

���C�g�f�[�^�ɑ��� C/BE[3:0]# �M���̃o�C�g�C�l�[�u���M�� be_n �̒l��ݒ�B

|

|

set_data_perr

|

std_logic

���C�g�f�[�^�ɑ���p���e�B�G���[��ݒ�B

�p���e�B�� PAR �� ����p���e�B�iOK�j�ɂ��邩�G���[�p���e�B�iNG�j�ɂ��邩��I������B

0�FOK�A�@1�FNG

|

|

���̑��̐M��

|

clk �ȉ��̐M���͖{procedure �ƊO���M����ڑ�����ׂ̂��́B

���[�U�̕ҏW�֎~�B

|

�i�S�j�������E���[�h�@pci_memory_read

procedure pci_memory_read (

set_address : in std_logic_vector(31 downto 0); --

set_ad_perr : in std_logic; -- 1: ng_parity, 0: ok_parity

set_be_n : in std_logic_vector(3 downto 0); --

----

signal clk : in std_logic; --

signal trdy_n : in std_logic; --

signal devsel_n : in std_logic; --

signal frame_n : out std_logic; --

signal ad : inout std_logic_vector(31 downto 0); --

signal c_be_n : out std_logic_vector(3 downto 0); --

signal irdy_n : out std_logic; --

signal par : inout std_logic; --

signal perr_n : out std_logic; --

signal sv_read_data : out std_logic_vector(31 downto 0) -- for test

);

| �ݒ荀�� |

�ݒ���e |

set_address

|

std_logic_vector(31 downto 0)

���[�h�Ώۂ̃A�h���X���w��B

|

set_ad_perr

|

std_logic

�A�h���X�ɑ���p���e�B�G���[��ݒ�B

�p���e�B�� PAR �� ����p���e�B�iOK�j�ɂ��邩�G���[�p���e�B�iNG�j�ɂ��邩��I������B

0�FOK�A�@1�FNG

|

set_be_n

|

std_logic_vector(3 downto 0)

���[�h�f�[�^�ɑ��� C/BE[3:0]# �M���̃o�C�g�C�l�[�u���M�� be_n �̒l��ݒ�B

|

|

���̑��̐M��

|

clk �ȉ��̐M���͖{procedure �ƊO���M����ڑ�����ׂ̂��́B

���[�U�̕ҏW�֎~�B

�Ȃ��Asv_read_data �̓��[�h�����f�[�^��Ղ��l�Ƃ��Ĕg�`�\������ׂ̂��̂ł���B

|

�i�T�jI/O�E���C�g�@pci_io_write

procedure pci_io_write (

set_address : in std_logic_vector(31 downto 0); --

set_ad_perr : in std_logic; -- 1: ng_parity, 0: ok_parity

set_wr_data : in std_logic_vector(31 downto 0); --

set_be_n : in std_logic_vector(3 downto 0); --

set_data_perr : in std_logic; -- 1: ng_parity, 0: ok_parity

----

signal clk : in std_logic; --

signal trdy_n : in std_logic; --

signal devsel_n : in std_logic; --

signal frame_n : out std_logic; --

signal ad : inout std_logic_vector(31 downto 0); --

signal c_be_n : out std_logic_vector(3 downto 0); --

signal irdy_n : out std_logic; --

signal par : inout std_logic --

);

| �ݒ荀�� |

�ݒ���e |

set_address

|

std_logic_vector(31 downto 0)

���C�g�Ώۂ̃A�h���X���w��B

|

set_ad_perr

|

std_logic

�A�h���X�ɑ���p���e�B�G���[��ݒ�B

�p���e�B�� PAR �� ����p���e�B�iOK�j�ɂ��邩�G���[�p���e�B�iNG�j�ɂ��邩��I������B

0�FOK�A�@1�FNG

|

set_wr_data

|

std_logic_vector(31 downto 0)

���C�g����f�[�^��ݒ�B

|

set_be_n

|

std_logic_vector(3 downto 0)

���C�g�f�[�^�ɑ��� C/BE[3:0]# �M���̃o�C�g�C�l�[�u���M�� be_n �̒l��ݒ�B

|

|

set_data_perr

|

std_logic

���C�g�f�[�^�ɑ���p���e�B�G���[��ݒ�B

�p���e�B�� PAR �� ����p���e�B�iOK�j�ɂ��邩�G���[�p���e�B�iNG�j�ɂ��邩��I������B

0�FOK�A�@1�FNG

|

|

���̑��̐M��

|

clk �ȉ��̐M���͖{procedure �ƊO���M����ڑ�����ׂ̂��́B

���[�U�̕ҏW�֎~�B

|

�i�U�jI/O�E���[�h�@pci_io_read

procedure pci_io_read (

set_address : in std_logic_vector(31 downto 0); --

set_ad_perr : in std_logic; -- 1: ng_parity, 0: ok_parity

set_be_n : in std_logic_vector(3 downto 0); --

----

signal clk : in std_logic; --

signal trdy_n : in std_logic; --

signal devsel_n : in std_logic; --

signal frame_n : out std_logic; --

signal ad : inout std_logic_vector(31 downto 0); --

signal c_be_n : out std_logic_vector(3 downto 0); --

signal irdy_n : out std_logic; --

signal par : inout std_logic; --

signal perr_n : out std_logic; --

signal sv_read_data : out std_logic_vector(31 downto 0) -- for test

);

| �ݒ荀�� |

�ݒ���e |

set_address

|

std_logic_vector(31 downto 0)

���[�h�Ώۂ̃A�h���X���w��B

|

set_ad_perr

|

std_logic

�A�h���X�ɑ���p���e�B�G���[��ݒ�B

�p���e�B�� PAR �� ����p���e�B�iOK�j�ɂ��邩�G���[�p���e�B�iNG�j�ɂ��邩��I������B

0�FOK�A�@1�FNG

|

set_be_n

|

std_logic_vector(3 downto 0)

���[�h�f�[�^�ɑ��� C/BE[3:0]# �M���̃o�C�g�C�l�[�u���M�� be_n �̒l��ݒ�B

|

|

���̑��̐M��

|

clk �ȉ��̐M���͖{procedure �ƊO���M����ڑ�����ׂ̂��́B

���[�U�̕ҏW�֎~�B

�Ȃ��Asv_read_data �̓��[�h�����f�[�^��Ղ��l�Ƃ��Ĕg�`�\������ׂ̂��̂ł���B

|

�i�V�j�������E�o�[�X�g�E���C�g�@pci_memory_burst_write

type SET_DATA is record

WR_DATA : std_logic_vector(31 downto 0);

BEn : std_logic_vector(3 downto 0);

PERR : std_logic; -- 1: ng_parity, 0: ok_parity

LAST : std_logic; -- 1: last data, 0: non-last data

end record;

type SET_DATA_ARRAY is array (0 to (MAX_DATA-1) ) of SET_DATA;

procedure pci_memory_burst_write (

set_address : in std_logic_vector(31 downto 0); --

set_ad_perr : in std_logic; -- 1: ng_parity, 0: ok_parity

set_data_array : in SET_DATA_ARRAY;

----

signal clk : in std_logic; --

signal trdy_n : in std_logic; --

signal devsel_n : in std_logic; --

signal frame_n : out std_logic; --

signal ad : inout std_logic_vector(31 downto 0); --

signal c_be_n : out std_logic_vector(3 downto 0); --

signal irdy_n : out std_logic; --

signal par : inout std_logic --

);

| �ݒ荀�� |

�ݒ���e |

set_address

|

std_logic_vector(31 downto 0)

���C�g�Ώۂ̐擪�A�h���X���w��B

|

set_ad_perr

|

std_logic

�A�h���X�ɑ���p���e�B�G���[��ݒ�B

�p���e�B�� PAR �� ����p���e�B�iOK�j�ɂ��邩�G���[�p���e�B�iNG�j�ɂ��邩��I������B

0�FOK�A�@1�FNG

|

set_wr_data

|

std_logic_vector(31 downto 0)

���C�g����f�[�^��ݒ�B

|

set_data_array

|

���C�g�f�[�^�����̃f�[�^���R�[�h�̔z��

pci_memory_burst_write �s���钼�O�ɗ\�ߏ������Ēu���B

�����VHDL���A�f�[�^���R�[�h�̓��e�� pci_memory_burst_write ���ɒ��ڋL�q�ł��Ȃ��d�l�ɂȂ��Ă���̂ŁA�ʓr�p�ӂ�����̂Ƃ����ׂł���B

�{�T�u�v���O�����ł͍ő�o�[�X�g�f�[�^���iMAX_DATA�j��4�ɂ��Ă���̂ŁA4�̃��R�[�h�̔z��Ƃ���B

��̓I�Ȏg�p��͌�o�̃e�X�g�x���`�̗�Q�ƁB

���\��1���R�[�h�̓��e�������B

| �ݒ荀�� |

�ݒ���e |

WR_DATA

|

std_logic_vector(31 downto 0)

���C�g����f�[�^��ݒ�B

|

BEn

|

std_logic_vector(3 downto 0)

���C�g�f�[�^�ɑ��� C/BE[3:0]# �M���̃o�C�g�C�l�[�u���M�� be_n �̒l��ݒ�B

|

PERR

|

std_logic

���C�g�f�[�^�ɑ���p���e�B�G���[��ݒ�B

�p���e�B�� PAR �� ����p���e�B�iOK�j�ɂ��邩�G���[�p���e�B�iNG�j�ɂ��邩��I������B

0�FOK�A�@1�FNG

|

LAST

|

std_logic

�ŏI���C�g�f�[�^���ǂ����ݒ�B

1: �ŏI�f�[�^�A 0: ��ŏI�f�[�^

4�̃��C�g�f�[�^�̃��R�[�h�z���LAST��1���ݒ肳�ꂽ�f�[�^�����C�g����B

�A���A4�S�Ă�LAST��0�̏ꍇ��4�̃f�[�^�����C�g����B

|

|

|

���̑��̐M��

|

clk �ȉ��̐M���͖{procedure �ƊO���M����ڑ�����ׂ̂��́B

���[�U�̕ҏW�֎~�B

|

�i�W�j�������E�o�[�X�g�E���[�h�@pci_memory_burst_read

subtype BEn is std_logic_vector(3 downto 0);

type BEn_ARRAY is array (0 to (MAX_DATA-1) ) of BEn;

procedure pci_memory_burst_read (

set_address : in std_logic_vector(31 downto 0); --

set_ad_perr : in std_logic; -- 1: ng_parity, 0: ok_parity

set_data_no : integer range 1 to MAX_DATA; --

set_be_n_array : in BEn_ARRAY; --

----

signal clk : in std_logic; --

signal trdy_n : in std_logic; --

signal devsel_n : in std_logic; --

signal frame_n : out std_logic; --

signal ad : inout std_logic_vector(31 downto 0); --

signal c_be_n : out std_logic_vector(3 downto 0); --

signal irdy_n : out std_logic; --

signal par : inout std_logic; --

signal perr_n : out std_logic; --

signal sva_read_data : out DATA_ARRAY -- for test

);

| �ݒ荀�� |

�ݒ���e |

set_address

|

std_logic_vector(31 downto 0)

���[�h�Ώۂ̐擪�A�h���X���w��B

|

set_ad_perr

|

std_logic

�A�h���X�ɑ���p���e�B�G���[��ݒ�B

�p���e�B�� PAR �� ����p���e�B�iOK�j�ɂ��邩�G���[�p���e�B�iNG�j�ɂ��邩��I������B

0�FOK�A�@1�FNG

|

set_data_no

|

integer range 1 to MAX_DATA

�o�[�X�g���[�h����f�[�^�����w��B

�{�T�u�v���O�����ł͍ő�o�[�X�g�f�[�^���iMAX_DATA�j��4�ɂ��Ă���̂ŁA�f�[�^����1�`4�Őݒ肷��B

|

set_be_n_array

|

BEn_ARRAY

���[�h�f�[�^�ɑ��� C/BE[3:0]# �M���̃o�C�g�C�l�[�u���M�� be_n �̒l�� BEn�istd_logic_vector(3 downto 0)�j

�̔z��Őݒ�B

�{�T�u�v���O�����ł͍ő�o�[�X�g�f�[�^���iMAX_DATA�j��4�ɂ��Ă���̂ŁA�z��̗v�f����1�`4�B

|

|

���̑��̐M��

|

clk �ȉ��̐M���͖{procedure �ƊO���M����ڑ�����ׂ̂��́B

���[�U�̕ҏW�֎~�B

�Ȃ��Asva_read_data �̓��[�h�����f�[�^��Ղ��l�Ƃ��Ĕg�`�\������ׂ̂��̂ł���B

|

�i�X�jPCI�C�j�V�����C�Y�@pci_init

procedure pci_init (

signal v_idsel : out std_logic_vector(31 downto 0); --

signal frame_n : out std_logic; --

signal ad : inout std_logic_vector(31 downto 0); --

signal c_be_n : out std_logic_vector(3 downto 0); --

signal irdy_n : out std_logic; --

signal par : inout std_logic; --

signal lock_n : out std_logic; --

signal req_n : out std_logic; --

signal perr_n : inout std_logic; --

signal serr_n : out std_logic; --

signal inta_n : out std_logic; --

signal intb_n : out std_logic; --

signal intc_n : out std_logic; --

signal intd_n : out std_logic --

);

| �ݒ荀�� |

�ݒ���e |

����

|

PCI�o�X�M���� signal��`�����Ŋe�M���̒l���������������ɁA�{�T�u�v���O������'Z'��'1'�ɃC�j�V�����C�Y������̂ŁA�g�p�͕K�{�ł͂Ȃ��B

�V�~�����[�V�����g�`�̐M�����x���s�蕔���i�ԐF�j�����A���h����ǂ�����ׂɗp�ӂ����B

�S�M�����{procedure �ƊO���M����ڑ�����ׂ̂��̂ł���A���[�U�̕ҏW�֎~�B

|

�@�ȏ�

�@�i���Ł@2018/11/28�j

�|�|�|�|�|�@�{�y�[�W�͂����܂Ł@�|�|�|�|�|

�@PCI�o�X�� 2002�N������ PCI Express�o�X�ɒu����������l�ɂȂ�A�ߔN�͗]��g�p����Ȃ��Ȃ����l�ł��A���i��������r�I�����Y�Ɨp�V�X�e���ł͌���ł������ł��B

�@PCI�o�X�� 2002�N������ PCI Express�o�X�ɒu����������l�ɂȂ�A�ߔN�͗]��g�p����Ȃ��Ȃ����l�ł��A���i��������r�I�����Y�Ɨp�V�X�e���ł͌���ł������ł��B

�@�}�Q�́A ModelSim ALTERA STARTER EDITION 10.1e Revision: 2013.06 (ALTERA)�̃v���W�F�N�g��ʂł��B

�@�}�Q�́A ModelSim ALTERA STARTER EDITION 10.1e Revision: 2013.06 (ALTERA)�̃v���W�F�N�g��ʂł��B

�@�ȉ��̎菇�Ŕ�r�I�e�ՂɃ��[�U��PCI�o�X�𐧌�ł��܂��B

�@�ȉ��̎菇�Ŕ�r�I�e�ՂɃ��[�U��PCI�o�X�𐧌�ł��܂��B ���T�u�v���O�����̉���

���T�u�v���O�����̉���